## CSE140L Final Exam, 3-4:30PM, Friday June 12, Name\_\_\_

- 1. Use CMOS complementary logic to implement the following functions. Draw the circuit to show your design.

- a) f(a) = a'.

b) f(a,b) = (a+b)'.

c) f(a,b,c) = [a(b+c)]'.

d) f(a,b,c)=[ab+(a+b)c]'

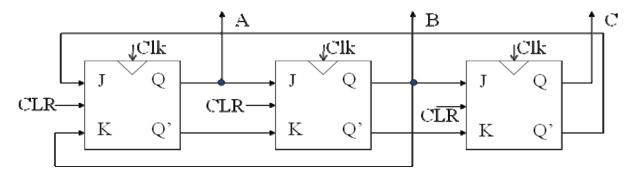

2. The logic diagram below shows a 3-bit counter. Derive the function behavior of the counter.

a) Suppose the flip-flops are reset initially, enumerate the states (A,B,C) according to the clock sequence. Fill the following table.

| Time | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|------|---|---|---|---|---|---|---|

| А    | 0 |   |   |   |   |   |   |

| В    | 0 |   |   |   |   |   |   |

| С    | 0 |   |   |   |   |   |   |

b) Suppose the flip-flops are not reset initially. Instead, the initial state is (A,B,C) = (0,1,0). Fill the following table.

| Time | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|------|---|---|---|---|---|---|---|

| А    | 0 |   |   |   |   |   |   |

| В    | 1 |   |   |   |   |   |   |

| С    | 0 |   |   |   |   |   |   |

| PS | x=0   | x=1  |

|----|-------|------|

| А  | F, 1  | B, 0 |

| В  | C, 0  | D, 1 |

| С  | A, 0  | E, 0 |

| D  | B, 0  | E, 1 |

| Е  | B, 1  | D, 1 |

| F  | С,0   | F,1  |

|    | NS, z |      |

3. Given a Mealy machine as described by the following state table. Transform the Mealy machine to a Moore machine. Write the state table.

| Command | 2-bit       | 4-bit                  | Description                                |

|---------|-------------|------------------------|--------------------------------------------|

|         | Instruction | Data                   |                                            |

| Move1   | 00          | $d_{3}d_{2}d_{1}d_{0}$ | Move data $d_3d_2d_1d_0$ to register R1.   |

| Move2   | 01          | $d_{3}d_{2}d_{1}d_{0}$ | Move data $d_3d_2d_1d_0$ to register R2.   |

| Add     | 10          | XXXX                   | Add R1 and R2, store the result back to    |

|         |             |                        | R1, and output the overflow flag.          |

| Branch  | 11          | $d_{3}d_{2}d_{1}d_{0}$ | Branch to instruction at address           |

|         |             |                        | $d_3d_2d_1d_0$ , if overflow flag is true. |

4. Assume a computer system has a simple instruction set described as follows:

a) Implement a datapath system to carry out the instructions. Assuming that you have two four-bit registers R1 and R2, one flip-flop for overflow\_flag, one 4-bit adder with overflow output, one counter for program branching, and one memory module which stores the instruction. Draw the logic diagram to illustrate your data path design. Label the signals of all the modules.

b) Implement the control subsystem. Use the truth table to describe the control subsystem design.