### CSE140 Discussion

Mingjing Chen 5/4

## 3.4 Sequential circuit check

| S | R | Q                 | Q'     | S'-Q                  |

|---|---|-------------------|--------|-----------------------|

| 0 | 0 | Q <sub>prev</sub> | Q'prev | Retain previous state |

| 0 | 1 | 0                 | 1      | reset R'-             |

| 1 | 0 | 1                 | 0      | set                   |

| 1 | 1 | 1                 | 1      | invalid               |

Still an SR latch

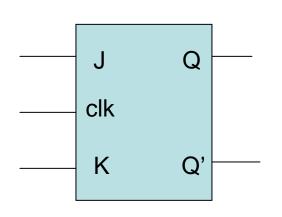

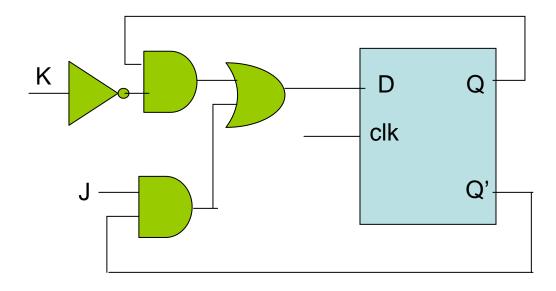

# 3.7 Flip-flop conversion: D→JK

| J | K | Q                 | Q'                |

|---|---|-------------------|-------------------|

| 0 | 0 | Q <sub>prev</sub> | Q'prev            |

| 0 | 1 | 0                 | 1                 |

| 1 | 0 | 1                 | 0                 |

| 1 | 1 | Q'prev            | Q <sub>prev</sub> |

| D | Q | Q' |

|---|---|----|

| 0 | 0 | 1  |

| 1 | 1 | 0  |

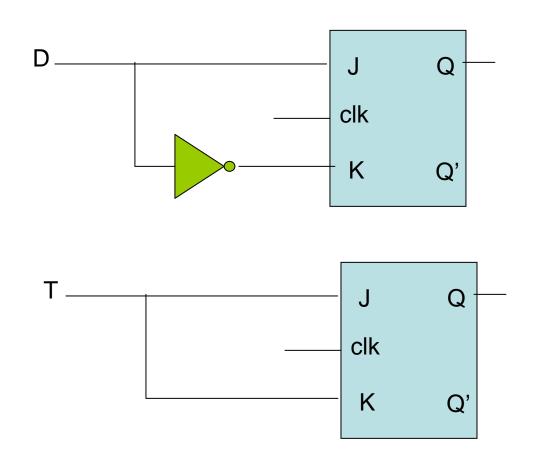

### 3.7 Flip-flop conversion: JK→D&T

Question:

$D \rightarrow T$

$T \rightarrow D$

## Sequential circuit design flow

#### <u>Step 1:</u>

Circuit specification → FSM

#### <u>Step 1:</u>

FSM Next state table. The table should show the present states, inputs, next states and outputs.

#### <u>Step 2:</u>

State encoding. If you have n states, your binary codes will have at least log<sub>2</sub> n digits, and your circuit will have at least log<sub>2</sub> n flip-flops.

#### <u>Step 3:</u>

Select flip-flop and create flip-flop excitation table. For each flip-flop and each row of your state table, find the flip-flop input values that generate the correct next state.

#### <u>Step 4:</u>

Find simplified equations for the flip-flop inputs and the outputs. You can use Kmap to derive each equation

#### <u>Step 5:</u>

**Build the circuit!**

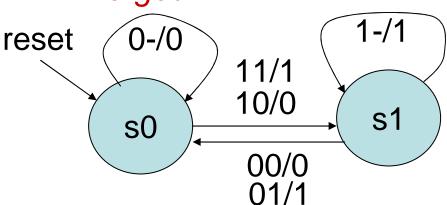

### Specification:

Input: A, B

Outputs: Z

$$Z_{n} = A_{n} A_{n-1}$$

, if  $B_{n} = 0$

$$Z_n = A_n + A_{n-1}$$

, if  $B_n = 1$

Is this FSM a Moore machine or Mealy machine?

Mealy machine, as the output depends on the input value

### Specification:

Input: A, B

Outputs: Z

$$Z_n = A_n A_{n-1}$$

, if  $B_n = 0$

$Z_{n} = A_{n} + A_{n-1}$ , if  $B_{n} = 1$

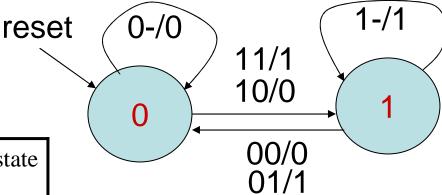

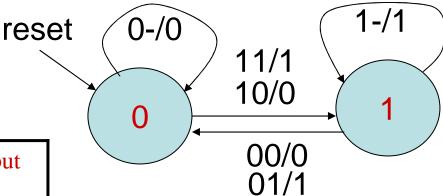

0-/0 reset 0-/0 s0 start 11/1 11/1 00/0 10/0 AB/Z 01/1 10/0 **s1** 1-/1

Draw the FSM diagram Idea: need two states for

memorizing  $A_{n-1}$

Can it be optimized?

No difference between Start & S0. They can be merged!

### Specification:

Input: A, B

Outputs: Z

$$Z_{n} = A_{n} A_{n-1}$$

, if  $B_{n} = 0$

$$Z_n = A_n + A_{n-1}$$

, if  $B_n = 1$

| A | В | Current state | Next state |

|---|---|---------------|------------|

| 0 | 0 | 0             | 0          |

| 0 | 0 | 1             | 0          |

| 0 | 1 | 0             | 0          |

| 0 | 1 | 1             | 0          |

| 1 | 0 | 0             | 1          |

| 1 | 0 | 1             | 1          |

| 1 | 1 | 0             | 1          |

| 1 | 1 | 1             | 1          |

State encoding

Next state equation:

$$Q_{next} = A$$

### Specification:

Input: A, B

Outputs: Z

$$Z_{n} = A_{n} A_{n-1}$$

, if  $B_{n} = 0$

$$Z_n = A_n + A_{n-1}$$

, if  $B_n = 1$

| A | В | Current state | output |

|---|---|---------------|--------|

| 0 | 0 | 0             | 0      |

| 0 | 0 | 1             | 0      |

| 0 | 1 | 0             | 0      |

| 0 | 1 | 1             | 1      |

| 1 | 0 | 0             | 0      |

| 1 | 0 | 1             | 1      |

| 1 | 1 | 0             | 1      |

| 1 | 1 | 1             | 1      |

State encoding

| A                      | AΒ |    |    |    |

|------------------------|----|----|----|----|

| 0                      | 00 | 01 | 11 | 10 |

| Q <sub>current</sub> 0 | 0  | 0  | 1  | 0  |

| 1                      | 0  | 1  | 1  | 1  |

Output equation: Z = AB+BQ+AQ

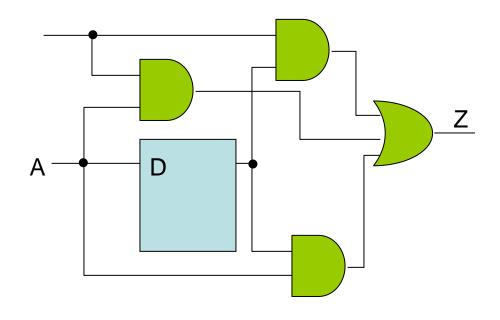

#### Specification:

Input: A, B

Outputs: Z

$$Z_n = A_n A_{n-1}$$

, if  $B_n = 0$

$$Z_n = A_n + A_{n-1}$$

, if  $B_n = 1$

Next state equation:

$Q_{next} = A$

Output equation:

Z = AB + BQ + AQ

Use D flip-flop

Question:

How to design the circuit using JK flip-flop?